doc.: IEEE 802.15-10-0435-01-004g

## Improved PHR coding of the MR-O-QPSK PHY

Michael Schmidt- ATMEL

July 6, 2010

doc.: IEEE 802.15-10-0435-01-004g

# IEEE P802.15 Wireless Personal Area Networks

Title: Improved PHR coding of the MR-O-QPSK PHY

Date Submitted: July 6, 2010

Source: Michael Schmidt - Atmel (email: michael.schmidt@atmel.com)

Re: Task Group 15.4g LB51 comment resolution

Abstract: Comment resolutions related to PHR coding of the MR-O-QPSK

PHY

Notice: This document has been prepared to assist the IEEE P802.15.

It is offered as a basis for discussion and is not binding on the contributing individual(s) or organization(s). The material in this document is subject to change in form and content after further study. The contributor(s) reserve(s) the right to add, amend or

withdraw material contained herein.

Release: The contributor acknowledges and accepts that this contribution

becomes the property of IEEE and may be made publicly available

by P802.15.

#### Motivation

This document describes the proposed resolution of LB51 on some comments related to MR-O-QPSK PHY regarding the PHY header (PHR).

The following comments are addressed:

▶ SFD length: CID # 879

▶ PHR error detection: CID # 890, 891, 912

► PHR FEC: CID # 1470

The following comments are partially addressed:

▶ Pilot sequences: CID # 1475

## Coding of PPDU scheme (780/915 MHz band)<sup>1</sup>

15.625 kbit/s: (no FEC) + (bit-diff enc) + (64,1)-DSSS 31.25 kbit/s: (rate 1/2 FEC) + (bit-diff enc) + (16,1)-DSSS

<sup>&</sup>lt;sup>1</sup>as specified for the MR-O-QPSK PHY in draft P802.15.4g/d1,March 2010

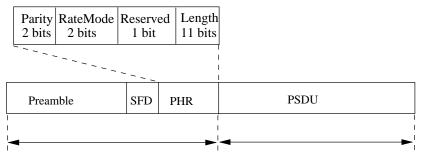

- ▶ Bits of Preamble, SFD and PHR field:

- no FEC

- bit-differential encoding (BDE)

- ► (N\*4,1)-DSSS

- ▶ Bits of the PSDU for the lowest data rate are:

- ▶ FEC: rate 1/2 convolutional coding, K = 7

- bit-differential encoding (BDE)

- ▶ (N,1)-DSSS

(SHR,PHR) and PSDU are approx. balanced with regard to the BER.

So why is there an issue?

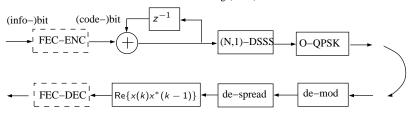

## Purpose of bit-differential encoding (BDE)

#### bit-differential encoding (BDE)

non-coherent demodulation

## Purpose of bit-differential encoding (BDE)

- ► low chip SNR

- exploit non-coherent detection

- no phase control loop required

- Note: at low SNR, a phase control loop may cause considerable noise enhancement.

- non-coherent demodulation <u>after</u> de-spreading in order to improve multi-path robustness

Consider a binary (32,8, $d_{min} = 13$ ) block code<sup>2</sup>

- code rate is 1/4

- ▶ optimal<sup>3</sup> minimum distance for a binary (32,8) linear code

- Soft-decision ML-decoding at moderate complexity (256 codewords only)

<sup>&</sup>lt;sup>2</sup>This code can be obtained from a (33,8,14)-code by puncturing position 33; see T. Helleseth & Ø. Ytrehus, How to find a [33,8,14] code, Report in Informatics (preliminary version), Dept. of Informatics, Univ. of Bergen, Norway, Nov. 1989.

<sup>&</sup>lt;sup>3</sup>see Markus Grassel http://www.codetables.de/

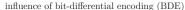

# Simulation, assuming perfect chip synchronization and phase<sup>4</sup>

<sup>&</sup>lt;sup>4</sup>relevant for coherent detection

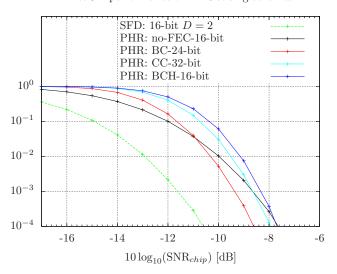

▶ There seems to be little performance difference between:

no-FEC

$$+$$

BDE  $+$  (4\*N,1)-DSSS and (32,8,13)-FEC  $+$  BDE  $+$  (N,1)-DSSS

All coding gain is eaten up by enhanced noise due to reduced spreading length.

But there is a gain!

▶ For real world applications, there is always a frequency offset

$$\Omega \left[ \operatorname{rad}/T_{chip} \right]$$

which cannot be perfectly estimated.

• A residual frequency offset  $r = \Omega - \hat{\Omega}$  causes phase drift

$$\tilde{x}(k) = \exp(jrk)x(k)$$

- ▶ Depending on *r*, de-spreading will result in loss of processing gain, when de-correlating against the known chip sequence.

- ▶ Clearly, a long DSSS sequence is prone to a residual error *r*.

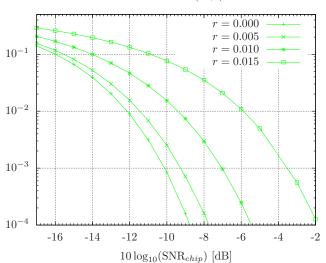

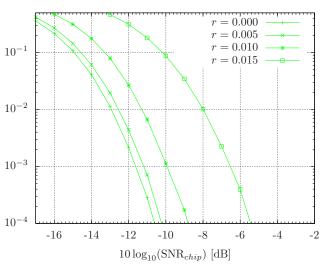

# Influence of residual frequency offset $r = \Omega - \hat{\Omega}$

no-FEC + BDE + (64,1)-DSSS

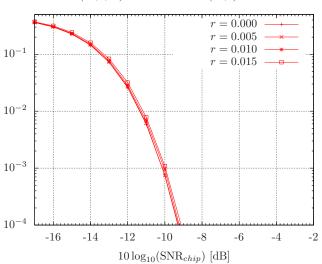

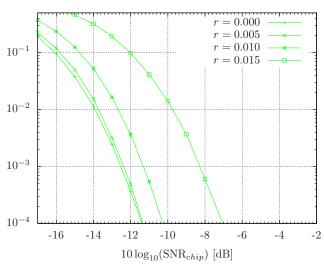

## Influence of residual frequency offset $r = \Omega - \hat{\Omega}$

(32,8,13)-FEC + BDE + (16,1)-DSSS

doc.: IEEE 802.15-10-0435-01-004g

#### What about the SFD?

- ▶ FEC cannot be conveniently applied to the SFD.

- ▶ Will this make PHR FEC useless?

#### Difference between SFD and PHR field

- During PHR detection, a single info-bit error (or more) usually causes a packet error.

- ▶ During SFD detection, a single info-bit error (or more) must not lead to a packet error.

Let  $A_D$  be the event of a correctly received word of length M

$$A_D: \|\mathbf{w} - \hat{\mathbf{w}}\| \leq D$$

#### where

- ▶ ||.|| is the Hamming distance

- ▶  $w \in GF(2^M)$  is transmitted word

- $\hat{w} \in GF(2^M)$  is the detected word

- ▶ D is the maximum number of allowed bit errors.

The complementary event  $\overline{A}_D$  is called a word error.

### Word Error Rate (WER) for D = 0

$$M = 16$$

$D = 0$ ; no-FEC + BDE + (64,1)-DSSS

### Word Error Rate (WER) for D=1

$$M = 16$$

$D = 1$ ; no-FEC + BDE + (64,1)-DSSS

word error rate (WER)

### Word Error Rate (WER) for D = 2

$$M = 16$$

$D = 2$ ; no-FEC + BDE + (64,1)-DSSS

## Word Error Rate (WER) for D = 3

$$M = 16$$

$D = 3$ ; no-FEC + BDE + (64,1)-DSSS

#### SFD candidates

- ▶ M = 16 bit rather than M = 8 bit SFD

- In order to allow bit errors during SFD search while preserving a low false alarm rate, the Hamming distance to zero-bit preamble sequence needs be optimized:

$$w^{opt} = \underset{w \in \mathit{GF}(2^M)}{\mathsf{arg-max}} \left\{ \underset{k \in 1,...,M}{\mathsf{min}} \| w - (\underbrace{0,...,0}_{k}, w_0,...,w_{M-k-1}) \| \right\}$$

For an SFD pair, two such SFD words need to be found with good Hamming distances to each other.

#### SFD candidates

► single<sup>5</sup> SFD

$$(w_0, w_1, ..., w_{15})^{opt} = (1, 1, 1, 0, 1, 0, 1, 1, 0, 1, 1, 0, 0, 0, 1, 0)$$

During search, distance to preamble is  $\geq 9$ .

good SFD pair

$$(w_0, w_1, ..., w_{15})^{opt} = (1, 1, 1, 0, 1, 0, 1, 1, 0, 1, 1, 0, 0, 0, 1, 0)$$

$(w_0, w_1, ..., w_{15})^{opt2} = (1, 1, 1, 1, 0, 1, 0, 1, 1, 0, 0, 1, 0, 0, 0, 0)$

During search, distance to preamble is  $\geq 8$  and  $||w^{opt} - w^{opt2}|| = 9$ .

$<sup>{}^{5}\</sup>underline{\mathsf{SpreadingMode}} \in \! \{\mathsf{DSSS}, \mathsf{MDSSS}\}$  cannot be indicated by the SFD value.

# Candidates for PHR coding and spreading (780/915 MHz band)

| Scheme                     | #    | FEC                        | Intrl.    | CRC-8 | DSSS   | #     |

|----------------------------|------|----------------------------|-----------|-------|--------|-------|

|                            | bits |                            |           |       |        | chips |

| no-FEC-16-bit <sup>6</sup> | 16   | no                         | no        | no    | (64,1) | 1024  |

| no-FEC-24-bit              | 24   | no                         | no        | yes   | (64,1) | 1536  |

| BC-16-bit                  | 16   | $(32,8,d_{min}=13)^7$      | no        | no    | (16,1) | 1024  |

| BC-24-bit                  | 24   | $(32,8,d_{min}=13)$        | no        | yes   | (16,1) | 1536  |

| CC-32-bit                  | 32   | $1/2 \text{ CC}^8 K = 7$   | yes(8x8)  | yes   | (16,1) | 1024  |

| CC-24-bit                  | 24   | $1/2 \ CC \ K = 7$         | yes(10×6) | yes   | (16,1) | 960   |

| BCH-16-bit                 | 16   | $BCH^9$ (63,16, $t = 11$ ) | no        | no    | (16,1) | 1008  |

$<sup>^{6}</sup>$ as specified in draft P802.15.4g/d1,March 2010

$<sup>^{7}</sup>$ applying ML-decoding with soft decisions on code bits

<sup>&</sup>lt;sup>8</sup>applying ML-Viterbi decoding with soft decisions on code bits

<sup>&</sup>lt;sup>9</sup>applying usual bounded minimum distance decoding with hard decisions on code bits

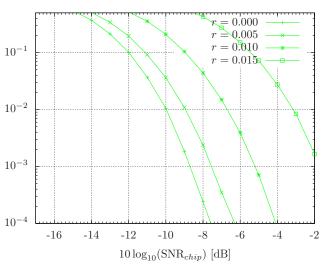

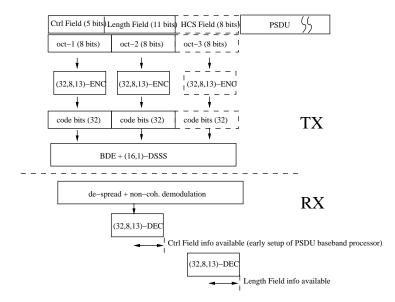

## BC-16/-24-bit: Rate 1/4 (32,8,13) Block Coding

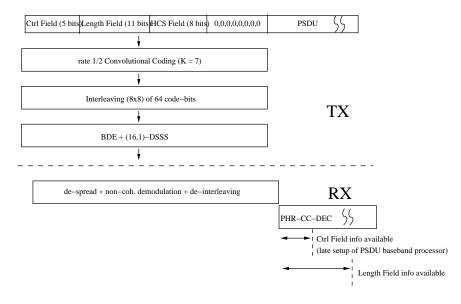

## CC-32-bit: Rate 1/2 Convolutional Coding with K = 7

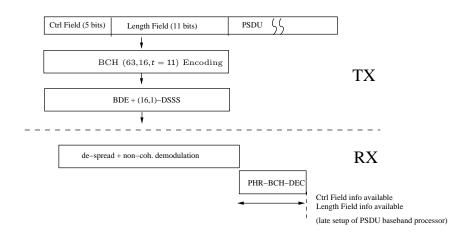

### BCH-16-bit: BCH (63,16,t=11)

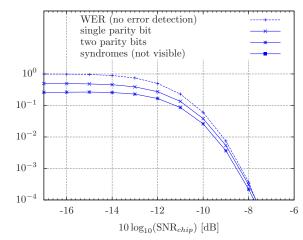

#### AWGN performance of PHR coding schemes

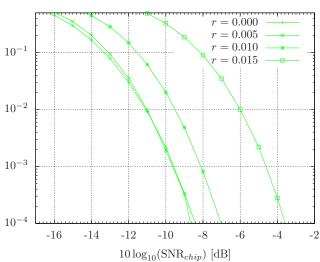

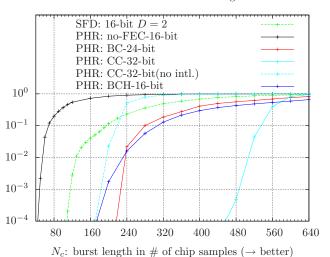

### Burst Errors: $N_c$ consecutive chip values blanked out

Word Error Rate (WER)

Burst Performance of PHR coding schemes

doc.: IEEE 802.15-10-0435-01-004g

#### Issues related to BC-24-bit:

▶ Inserting a CRC-8 based HCS causes more overhead compared to CC-32 (i.e. 1536 chip samples versus 1024 chip samples).

#### Issues related to CC-32-bit and BCH-16-bit:

- ▶ In contrast to the (32,8,13) code (processing data octet by octet), it is not possible to access reliable information of the Control field before all chip samples belonging to the PHR field are received.

- Consequently, chip samples belonging to the PSDU part need to be buffered while decoding the PHR field.

- ► The buffer size depends on the processing delay of the PHR FEC decoder.

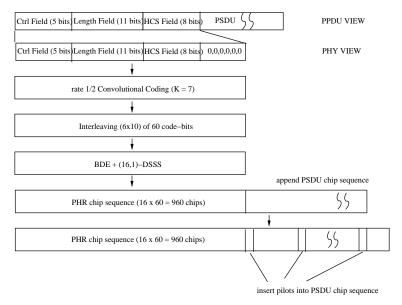

## CC-24-bit: Rate 1/2 Convolutional Coding with K = 7

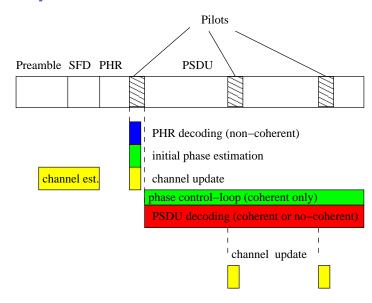

#### Pilot symbols

#### Pilot symbols

- first pilot:

- breathing space for PHR-FEC decoding

- simplifies initial phase estimation<sup>10</sup>

- simplifies initial channel estimation

- following pilots:

- supports channel tracking for long packets when combined with equalization (500 kbit/s PSDU data rate)

- supports timing point tracking for long packets (all PSDU data rates)

$<sup>^{10}\</sup>mbox{used}$  for coherent detection of (N,4)-DSSS or (N,8)-MDSSS during PSDU

## Candidates for pilot symbols (780 / 915 MHz band)

| pilot length # chips | pilot duration [us] | inter pilot spacing # chips |

|----------------------|---------------------|-----------------------------|

| 32x4 = 128           | 128                 | 2048                        |

| 16x4 = 64            | 64                  | 1024                        |

- Assuming a 16-MHz processing clock, this implies 1024 and 2048 processing cycles, respectively.

- ▶ This keeps FEC decoder complexity at a moderate level.

- Pilot sequence shall support simple correlation based channel estimation.

- Reasonable inter pilot spacing with regard to expected coherence time while keeping data rate loss due to overhead small (approx. 6%)

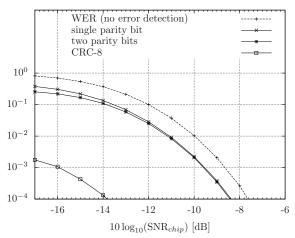

#### PHR Error Detection

- reduces sync on frames with incorrectly decoded Ctrl or Length field information

- may cause overhead

- ▶ let E be the event a detected PHR field error

- ▶ let  $\overline{E}\&\overline{A_0}$  be the event a non-detected PHR field error and the PHR Filed was incorrectly received

- ▶ let FAR (False Alarm Rate) denote the rate of occurrence of the event  $\overline{E}\&\overline{A_0}$

- clearly, FAR = WER if no Error detection capability can be exploited

#### Candidates for PHR Error Detection

- ▶ single parity check bit PHR(0) over PHR(1:15)

- ▶ two parity check bits<sup>11</sup> PHR(0:1) over PHR(2:8) and PHR (9:15), respectively

- ► CRC-8 based HCS<sup>12</sup> with generator polynomial  $X^8 + X^2 + X + 1$

- implicitly for BCH code (syndrome check)

<sup>&</sup>lt;sup>11</sup>as specified for the MR-O-QPSK PHY in draft P802.15.4g/d1,March 2010

<sup>&</sup>lt;sup>12</sup>similar to the OFDM PHY in draft P802.15.4g/d1,March 2010

Performance of Error Detection: no FEC-16/24-bit

Two parity check bits: poor CRC-8: good

Two parity check bits: poor CRC-8: good

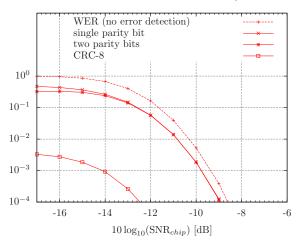

#### Performance of Error Detection: CC-24-bit

Two parity check bits: poor CRC-8: good

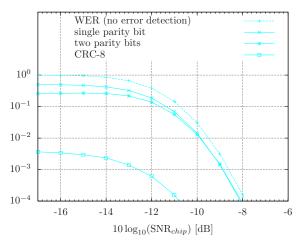

Two parity check bits: poor Syndromes: nearly perfect<sup>13</sup>

$<sup>^{13}</sup>$ The BCH-(63,16,t = 11) code has a generator polynomial of degree 47.

| Scheme        | advantage                                                                                                                           | disadvantage                                                                                                                                  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| No-FEC-16-bit | <ul><li>simple detection</li><li>early access to Ctrl field<br/>(bit-by-bit)</li></ul>                                              | <ul> <li>detection prone to<br/>frequency estimation and<br/>burst errors</li> <li>poor error detection (two<br/>parity bits)</li> </ul>      |

| No-FEC-24-bit | <ul> <li>simple detection</li> <li>early access to Ctrl field<br/>(bit-by-bit)</li> <li>good error detection<br/>(CRC-8)</li> </ul> | <ul> <li>detection prone to<br/>frequency estimation and<br/>burst errors</li> <li>error detection: CRC-8<br/>causes more overhead</li> </ul> |

| Scheme    | advantage                                                         | disadvantage              |

|-----------|-------------------------------------------------------------------|---------------------------|

| BC-16-bit |                                                                   |                           |

|           | robust detection                                                  | poor error detection (two |

|           | <ul><li>early access to Ctrl field<br/>(octet by octet)</li></ul> | parity bits)              |

|           | simple decoder                                                    |                           |

| BC-24-bit |                                                                   |                           |

|           | robust detection                                                  | error detection: CRC-8    |

|           | <ul><li>good error detection<br/>(CRC-8)</li></ul>                | causes more overhead      |

|           | <ul><li>early access to Ctrl field<br/>(octet-by-octet)</li></ul> |                           |

|           | simple decoder                                                    |                           |

| Scheme       | advantage                                                                                                                                                                     | disadvantage                                                                                                                                                                                                          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CC-24/32-bit | <ul> <li>very robust detection</li> <li>complex hardware of         PSDU FEC decoder can         be reused     </li> <li>good error detection         (CRC-8)     </li> </ul> | <ul> <li>late access to Ctrl field</li> <li>PSDU chip buffering<br/>required (unless pilots are<br/>prepended)</li> </ul>                                                                                             |

| BCH-16-bit   | <ul> <li>detection: sufficiently robust</li> <li>error detection: nearly perfect (syndromes)</li> <li>syndrome computation can already be performed during receive</li> </ul> | <ul> <li>late access to Ctrl field</li> <li>additional complex         <ul> <li>hardware for FEC</li> <li>decoder required</li> </ul> </li> <li>PSDU chip buffering required (unless pilots are prepended)</li> </ul> |

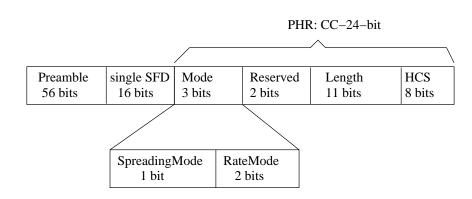

#### Recommendation

- CC-24-bit (terminated convolutional coding)

- proven approach (similar to IEEE 802.11a/g, TG4g OFDM PHY)

- 3 octets (24 info bits), while hiding 6 bit termination from the PPDU view

- termination supports fast traceback

- hardware for PSDU FEC can be reused

- CRC-8 based HCS

- sufficiently robust

- can be nicely integrated into CC-24-bit

- extend SFD to 16 bit: reduce preamble by one octet in order to sustain overall SHR length

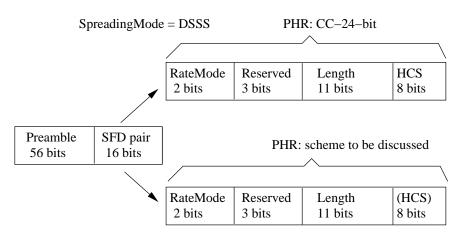

## Recommendation A: SpreadingMode distinguished by SFD

SpreadingMode = MDSSS

## Recommendation B: SpreadingMode indicated by PHR bit

#### Conclusions

▶ PHR processing based on pure spreading without FEC is prone to frequency estimation errors and burst errors.

#### PHR FEC is highly recommended!

- ▶ In order to benefit from PHR FEC, the uncoded SFD field should be extended 16 bits. This allows up to 3 SFD bit errors while keeping the false alarm rate low.

- Periodical insertion of <u>pilots</u> to the PSDU part is very useful for phase estimation, tracking and equalization. Decoding complexity of PHR FEC can be relaxed when prepending a first pilot sequences at the beginning of the PSDU part.

- ▶ PHR error detection based on 1 or 2 parity check bits is insufficient, especially in conjunction with FEC.